探索芯片集成创新路径与未来应用前景

我们正站在一个计算能力爆发的时代门口,而推动这一切的幕后英雄,除了我们熟知的芯片本身,还有一个越来越关键的角色——芯片封装技术,过去,封装只是简单地给芯片核心穿上一件“保护外衣”,再通过细细的金属线连接到电路板上,任务简单明确,但现在,情况完全不同了,封装技术已经从一个被动的保护者,演变为决定芯片性能、功耗和成本的主动设计核心,开启了一个全新的技术纪元。

这个转变的根本原因在于,单一芯片的性能提升正面临巨大的挑战,就像在一块田地里精耕细作,产量总有上限,科学家们发现,与其耗尽心力去雕刻一个巨大而复杂的单一芯片,不如换个思路:将多个较小、更专精的芯片单元,像搭乐高积木一样,巧妙地组合在一起,让它们协同工作,实现甚至超越单一巨无霸芯片的功能,这种思路,就是所谓的“芯片集成”或“异构集成”,而实现这种集成的关键,正是先进的封装技术。

这些新的封装技术究竟“新”在哪里?它们又是如何创新的呢?

是连接方式的革命,传统的金属线连接就像老式的电话线,距离长、速度慢、容易受干扰,新的技术,硅通孔”技术,相当于在芯片内部修建了垂直的“高速公路”,它通过在硅片本身打上微小的孔并填充导电材料,让上下堆叠的芯片可以直接、快速地进行垂直通信,大大缩短了信号传输的距离,速度更快,能耗更低。

是集成维度的突破,以前的芯片都是平铺在电路板上,占据很大面积,封装技术开始向三维空间发展,也就是我们常说的3D堆叠,这就像把平房改建成摩天大楼,在同样的“地基”(封装面积)上,容纳了数倍的计算单元,可以将处理器芯片、内存芯片等垂直堆叠在一起,处理器需要数据时,无需长途跋涉到主板上的内存条去取,直接从楼下的“邻居”(堆叠的内存)获取,效率得到质的飞跃。

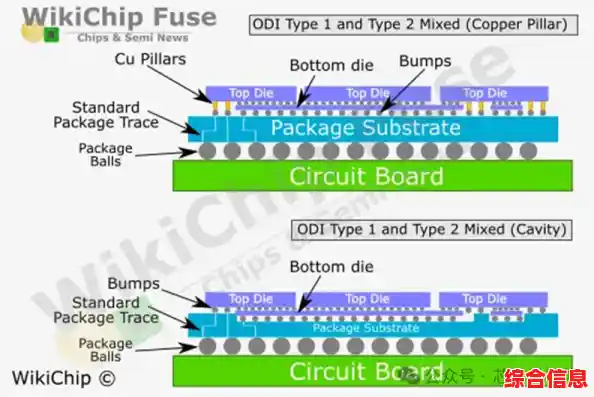

是材料和结构的创新,为了将不同工艺、不同功能(比如逻辑计算、模拟信号处理、射频通信)的芯片更紧密、更高效地集成在一起,新的封装技术采用了更先进的基板材料(如硅基板、玻璃基板),并发展出“扇出型”等全新结构,这就像为芯片们建造了一个规划更合理、基础设施更完善的“微型城市”,确保电力供应充足,信息流通顺畅,各单元既能紧密协作又互不干扰。

这些创新路径,正在为我们勾勒出未来芯片,乃至整个电子产业的广阔应用前景。

最直接的影响就是人工智能和高性能计算,AI模型越来越大,对计算速度和内存带宽的要求近乎贪婪,通过3D堆叠技术,可以将专用的AI计算芯片与高带宽内存紧密集成,彻底打通数据供给的“任督二脉”,使得AI训练和推理的速度得到指数级提升,让我们能处理更复杂的图像识别、自然语言处理等任务。

在消费电子领域,未来的智能手机、笔记本电脑和AR/VR设备将变得更加轻薄,但功能却更加强大,借助先进封装,可以在极小的空间内集成5G/6G通信模组、多种传感器、高效能处理器和超大容量电池,实现更长的续航和更沉浸式的体验,设备可以更小巧,但“内心”更强大。

在自动驾驶汽车中,需要实时处理海量的传感器数据(摄像头、激光雷达、雷达等),通过异构集成,可以将多个处理单元(CPU、GPU、AI加速器)集成在一个封装内,实现高效、低延迟的数据融合与决策,极大地提升自动驾驶系统的安全性和可靠性。

甚至在未来,我们可能会看到“系统级封装”的普及,即将一整个电子系统所需的所有功能,包括处理器、内存、电源管理、传感器等,全部集成到一个封装模块中,这就像购买一个“功能黑盒”,开发者无需关心内部复杂的电路,直接调用其功能即可,这将极大降低硬件开发门槛,加速物联网、可穿戴设备等创新应用的涌现。

这个新纪元也伴随着挑战,比如散热问题(摩天大楼里的“居民”如何高效散热)、测试难度(如何确保堆叠中每一层芯片都完美无缺)、以及成本控制,但毫无疑问,封装技术的创新已经不再是配角,它正与芯片设计、制造工艺并肩前行,共同推动着我们步入一个万物智能、算力无处不在的未来,它让“更多、更快、更小、更省电”的芯片梦想,拥有了实现的坚实路径。