谈论科技的发展,尤其是我们每天握在手中的手机、工作时面对的电脑,甚至是逐渐走入家庭的智能设备,都绕不开一个核心的词汇:芯片,这颗小小的、通常被金属外壳包裹的硅片,是现代数字世界的“大脑”和“心脏”,而衡量这颗“大脑”能力的关键,就在于其内部晶体管的尺寸,我们通常用“纳米”这个极小的单位来衡量,这就催生了一种直观的对比方式——我们可以将其想象成一个“纳米级芯片天梯图”。

这个天梯图,形象地描绘了芯片制造工艺数十年来一路向上攀登的历程,它不是一个简单的排名,更像是一部浓缩的科技进化史,记录着人类如何一次次挑战物理极限,将更多的晶体管塞进同样大小的空间里,回顾过去,我们曾站在“微米时代”的台阶上,那时的工艺还相对“粗糙”,但进入21世纪后,攀登的速度骤然加快,“纳米级”的竞赛正式拉开帷幕。

早期的台阶,比如90纳米、65纳米,对于当时来说已经是巨大的飞跃,它们让个人电脑真正普及,让功能手机开始向智能手机演变,但真正的白热化竞争,是从28纳米这个关键节点开始的,这个工艺节点成为了一个分水岭,在性能、功耗和成本之间找到了一个绝佳的平衡点,至今仍在许多对性能要求不高的领域广泛应用,从那时起,攀登天梯图的每一步都变得异常艰难。

紧接着,20纳米、16/14纳米工艺的出现,让移动互联网迎来了爆发,我们的手机变得前所未有的强大和智能,能够流畅处理高清视频、运行复杂的应用程序,同时电池续航也得到了显著改善,这背后,正是芯片晶体管密度成倍增加、能效比不断提升的结果。

当工艺进入10纳米、7纳米时代,天梯图的坡度变得更加陡峭,传统的技术路线开始遇到瓶颈,科学家和工程师们不得不引入全新的技术,比如FinFET(鳍式场效应晶体管),像建摩天大楼一样让晶体管“站立”起来,以更好地控制电流,减少漏电和功耗,这个阶段的芯片,直接推动了人工智能、5G通信和高性能计算的实质性突破,手机能够实时进行复杂的图像识别,自动驾驶技术看到了落地的曙光。

而当前我们正身处和奋力攀登的,是5纳米和3纳米的高阶台阶,到了这个尺度,已经逼近了物理规律的极限,芯片内部的结构复杂程度堪比一座超级大都市的立体交通网,每一平方毫米的面积上,都密集分布着数以亿计的晶体管,为了实现这一目标,更复杂的技术如EUV(极紫外光刻)成为了必不可少的“登山杖”,它用波长极短的光线,像最精细的刻刀一样,在硅片上雕刻出纳米级别的电路,处于这个台阶的芯片,为我们带来了前所未有的计算性能,让实时高清渲染、复杂的科学模拟等成为可能,同时也将设备的能效推向了新高度,意味着在完成同样任务时,电量消耗得更少。

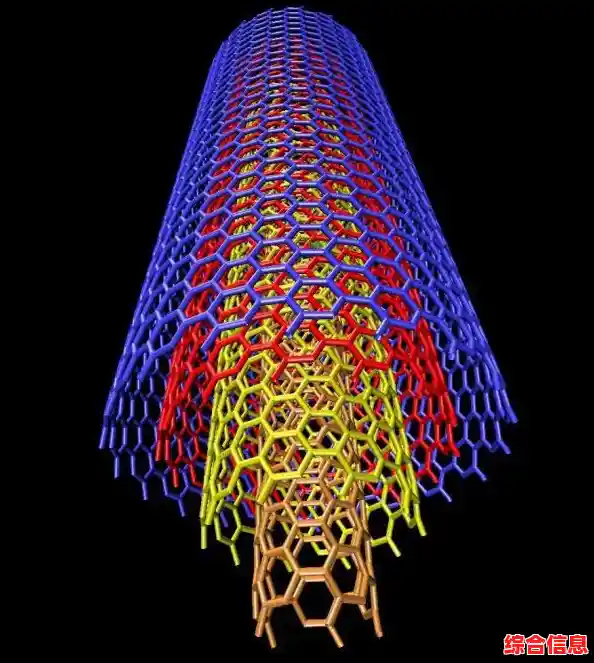

天梯图的攀登并未止步,展望未来,2纳米、1.5纳米甚至更先进的工艺节点已经出现在蓝图之上,但前方的道路充满了更大的挑战,当晶体管的尺寸小到只有几个原子的大小,量子隧穿等量子效应会带来难以控制的漏电问题,传统的硅材料也可能达到其物理极限,这就需要攀登者们寻找全新的路径和工具,比如转向全新的晶体管结构(如GAA环绕栅极技术),探索硅以外的半导体材料(如二维材料、碳纳米管),甚至从根本上改变计算范式(如量子计算、类脑计算)。

这张不断向上延伸的纳米级芯片天梯图,不仅仅是冰冷的技术参数堆砌,它实实在在地驱动着整个科技革命的进程,每一次工艺的进步,都意味着我们的电子设备更快一点、更智能一点、续航更长一点;都意味着数据中心能更高效地处理全球信息,减少巨大的能源消耗;都意味着医疗诊断更精准、科学研究工具更强大、我们探索未知世界的能力更进一步,它正引领我们坚定地迈向一个更高性能与更优能效的时代,而这个时代的终点,远未到来。