快科技揭示最新CPU性能飙升的核心奥秘

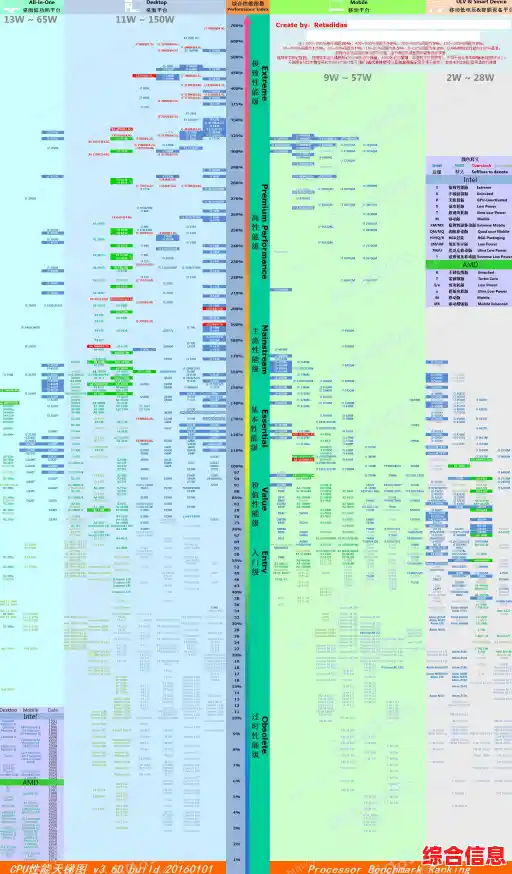

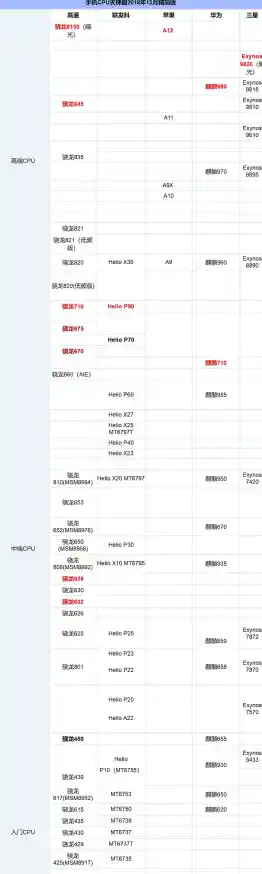

当我们打开一份最新的CPU性能天梯图,最直观的感受可能就是:顶端的处理器性能又比去年强了一大截,那一根根代表不同型号CPU的柱状图,就像不断向上攀爬的阶梯,记录着计算能力一次又一次的飞跃,这种看似按部就班的性能提升,背后其实是一场由多种核心驱动力共同作用的激烈竞赛,天梯图不仅仅是排名的罗列,更是解码这场竞赛奥秘的一把钥匙。

如果我们把时间线拉长,对比几年前的天梯图,会发现一个有趣的现象:早期处理器的性能提升,很大程度上依赖于一个叫做“制程工艺”的进步,就是制造CPU的精细度,这就像用笔画线,笔尖越细,在同一块地方就能画出更复杂、更密集的电路,更精细的工艺意味着可以在同样大小的芯片里塞进更多的晶体管(CPU的基本计算单元),让它们跑得更快、更省电,过去很长一段时间,我们习惯了每年制程工艺的数字变小,性能随之稳定增长的天梯图走势。

但最近几年,情况发生了显著变化,天梯图顶端处理器之间的性能差距有时会突然拉大,这不仅仅是制程工艺的功劳,奥秘的核心转向了“架构”的彻底革新,架构可以理解为CPU的设计蓝图,一个优秀的架构,就像一位天才工程师设计的发动机,即使用同样的材料和工艺,也能爆发出远超同行的马力,芯片设计者们不再满足于简单地增加晶体管数量,而是开始重新思考如何让这些晶体管更聪明、更高效地协同工作。

其中一个关键策略就是“分工细化”,早期的CPU核心像是一个什么活都干的工人,虽然努力,但效率有瓶颈,现在的处理器普遍采用了“大小核”的混合架构,这就像一支团队,有负责高强度计算、追求极致速度的“大核”(性能核),也有负责日常轻量任务、极其省电的“小核”(能效核),当你运行游戏或进行视频剪辑时,大核全力冲刺;当你后台听音乐、收发邮件时,小核默默工作,保证流畅的同时极大降低了功耗,这种设计让CPU在面对复杂多任务时变得更加游刃有余,在天梯图的多线程性能测试中表现尤为突出。

另一个推动性能飙升的奥秘是“缓存”的急剧扩大和智能化,缓存是CPU内部的高速临时仓库,用来存放最急需处理的数据,如果CPU每次计算都要去遥远的内存里取数据,就会浪费大量时间等待,最新的处理器大幅增加了各级缓存的容量,尤其是共享缓存,让多个核心能更快地交换数据,这好比在繁忙的厨房里,给每位大厨(核心)都配了一个超大的备料台(缓存),并且还有一个共享的中央食材库,大大减少了来回跑动取料的时间,做菜(计算)效率自然飞速提升,天梯图中,那些缓存巨大的处理器,在游戏和专业应用中的表现往往一骑绝尘。

我们不能忽视“集成与互联”的力量,现在的CPU早已不是一颗孤立的芯片,它内部往往还集成了高性能的显卡、AI加速引擎、以及负责高速连接内存和硬盘的控制器,更重要的是,连接这些内部模块的“高速公路”也得到了前所未有的升级,更宽、更快的内部总线,确保了数据在CPU内部以及CPU与周边设备之间能够极速流转,减少了瓶颈,这就好比一个城市,不仅修建了更强大的核心建筑(CPU核心),还同步升级了所有的道路和交通枢纽(互联架构),使得整个系统的运行效率倍增,这种整体优化带来的体验提升,同样被天梯图的综合性能评分所捕捉。

驱动这一切成为可能的,是强大的“设计工具与算法”,借助先进的EDA(电子设计自动化)软件和人工智能,工程师们可以在虚拟环境中模拟和优化数以亿计的晶体管布局,找到最优解,这在过去是不可想象的,AI甚至能够参与设计过程,探索人类工程师可能忽略的架构可能性,这种设计能力的进化,是推动CPU架构持续创新、性能不断突破天花板的基础。

当我们再次审视那张不断更新的CPU天梯图时,看到的不仅仅是冷冰冰的性能分数和排名,它更像是一幅动态的技术演进地图,清晰地展示了处理器进化之路如何从单纯追求工艺微缩,转向了架构创新、精细化分工、缓存策略、系统集成和设计方法论等多维度、深层次的综合较量,性能的每一次飙升,都是这些核心奥秘被逐一破解和深度融合的结果,而未来的天梯图,必将由更多这样的创新继续书写。